sigmafullpac

4 Bit Parallel In Serial Out Shift Register Verilog Code

- 4 Bit Parallel In Serial Out Shift Register Verilog Code For 10

- Verilog Code For Piso Shift Register Using D Flip Flop

- Serial In Serial Out Shift Register Pdf

IntroductionIn previous chapters, some simple designs were introduces e.g. Mod-m counter and flip-flops etc. To introduce the Verilog programming. In this chapter various examples are added, which can be used to implement or emulate a system on the FPGA board.All the design files are provided inside the ‘VerilogCodes’ folder inside the main project directory; which can be used to implement the design using some other software as well. Each section shows the list of Verilog-files require to implement the design in that section. Lastly, all designs are tested using Modelsim and on Altera-DE2 FPGA board. Set the desired design as ‘top-level entity’ to implement or simulate it.

// randnumgeneratorvisualTest.v // created by: Meher Krishna Patel // date: 22-Dec-16 // if parameter value is changed e.g. N = 5 // then go to randnumgenerator for further modification module randnumgeneratorvisualTest #( parameter N = 3 ) ( input wire CLOCK50, reset, output wire N: 0 LEDR ); wire clkPulse1s; // clock 1 s clockTick #(.

M ( 50000000 ),. N ( 26 )) clock1s (. Clk ( CLOCK50 ),. Reset ( reset ),.

ClkPulse ( clkPulse1s )); // randnumgenerator testing with 1 sec clock pulse randnumgenerator randnumgenerator1s (. Clk ( clkPulse1s ),. Reset ( reset ),.

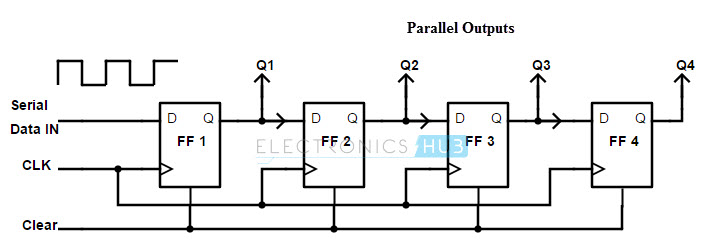

Q ( LEDR ) ); endmodule. Shift registerShift register are the registers which are used to shift the stored bit in one or both directions. In this section, shift register is implemented which can be used for shifting data in both direction. Further it can be used as parallel to serial converter or serial to parallel converter. Verilog files required for this example are listed below,. shiftregister.v. shiftregistervisualTest.v.

clockTick.v. modMCounter.v. paralleltoserial.v. serialtoparallel.v.

parallelandserialtop.v. parallelandserialtopvisual.vNote that, ‘clockTick.v’ and ‘modMCounter.v’ are discussed in Chapter. In the listing, the ‘ctrl’ port is used for ‘shifting’, ‘loading’ and ‘reading’ data operation. Lines 28 clear the shift register during reset operation, otherwise go to the next state.Lines 35-40 perform various operations based on ‘ctrl’ values. Note that, to perform right shift (Line 37), data is continuously provided from last port i.e. (data(N-1)); whereas for left shift (Line 38) data is provided from first port i.e. (data(0)).Next, ctrl=‘00’ is provided for reading the data.

It can be used for serial to parallel conversion i.e. When all the bits are shifted and register is full; then set ctrl to ‘00’ and read the data, after that set ctrl to ‘01’ or ‘10’ for getting next set of bits.Similarly, for parallel to serial converter, first load the data using ctrl=‘11’; and then perform the shift operation until all the bits are read and then again load the data. Note that, in this case, last bit propagates (i.e. Data(N-1) for right shift or data(0) for left shift) during shifting; which is actually designed for serial to parallel converter. But this will affect the working of parallel to serial converter, as we will set ctrl to ‘11’, when all the data is shifted, therefore all the register which were filled by values from last port, will be overwritten by the new parallel data.Lastly, data is available on the output port ‘qreg’ from Line 43. For, parallel to serial converter, use only one pin of ‘qreg’ i.e.

Qreg(0) for right shift or q(N-1) for left shift; whereas for serial to parallel conversion, complete ‘qreg’ should be read.Fig. Shows the shifting operation performed by the listing. Here first data ( i.e. 00110000) is loaded with ctrl=‘11’. Then shifted to right after first cursor and later to the left i.e.

After second cursor. // shiftregistervisualTest.v // created by: Meher Krishna Patel // date: 22-Dec-16 // SW16:15: used for control module shiftregistervisualTest #( parameter N = 8 ) ( input wire CLOCK50, reset, input wire 16: 0 SW, output wire N - 1: 0 LEDR ); wire clkPulse1s; // clock 1 s clockTick #(. M ( 50000000 ),.

N ( 26 )) clock1s (. Clk ( CLOCK50 ),. Reset ( reset ),. ClkPulse ( clkPulse1s )); // shiftregister testing with 1 sec clock pulse shiftregister #(. N ( N )) shiftregister1s (.

Clk ( clkPulse1s ),. Reset ( reset ),. Data ( SW N - 1: 0 ),. Ctrl ( SW 16: 15 ),.

Qreg ( LEDR ) ); endmodule. // serialtoparallel.v // converts serial data to parallel module serialtoparallel #( parameter N = 8 ) ( input wire clk, reset, input wire datain, // serial data output wire fulltick, // for external control output reg N - 1: 0 dataout // parallel data ); reg N - 1: 0 datareg, datanext; reg N - 1: 0 countreg, countnext; reg fullreg, fullnext; // register is full i.e.

Parallel data is ready to read assign fulltick = fullreg; // save initial and next value in register always @( posedge clk, posedge reset ) begin if ( reset ) begin countreg. Test for Parallel/Serial convertersHere, 4-bit count (i.e. Parallel data) is generated using Mod-12 counter.

This data is converted into serial data by; and sent to, where data is again converted into parallel and the result (i.e. Count) is displayed at output as shown in. The simulation results are shown in Fig. Lastly, visual verification circuit is shown in. Note that, emptytick signal is used as clock for modMCounter (see red line in Fig.:numref:`figparallelandserialdesign`), so that next count will be available when previous conversion is completed. Please read comments for further details. // parallelandserialtop.v // test paralleltoserial.v and serialtoparallel.v // parallel data (i.e.

Count from modMCounter) is converted into // serial data using paralleltoserial.v then tranmitted. // Next, transmitted data is received at serialtoparallel.v and // converted back to parallel. If everything is working properly then // count should be displayed on 'outcount'. Module parallelandserialtop ( reset, clk, outcount ); input wire reset; input wire clk; output wire 3: 0 outcount; wire eclk; wire 3: 0 parallelcount; wire serialcount; // count from modMCounter modMCounter unitcounter (. Clk ( eclk ),.

Msh brain pc software. Reset ( reset ),. Count ( parallelcount )); defparam unitcounter.

M = 12; defparam unitcounter. N = 4; // count converted into serial data paralleltoserial unitps (.

Clk ( clk ),. Reset ( reset ),. Datain ( parallelcount ),. Emptytick ( eclk ),. Dataout ( serialcount )); defparam unitps. N = 4; // serial data converted back to parallel data serialtoparallel unitsp (. Clk ( clk ),.

Reset ( reset ),. Datain ( serialcount ),. Dataout ( outcount )); defparam unitsp. N = 4; endmodule. // parallelandserialtopvisual.v // visual test for parallelandserialtop.v module parallelandserialtopvisual ( reset, CLOCK50, LEDG ); input wire reset; input wire CLOCK50; output wire 3: 0 LEDG; wire clk1ms; // parallelandserialtop parallelandserialtop unitpstop (. Reset ( reset ),. Clk ( clk1ms ),.

Outcount ( LEDG )); // 1 ms clock clockTick unitclk1ms (. Clk ( CLOCK50 ),. Reset ( reset ),. ClkPulse ( clk1ms )); defparam unitclk1ms. M = 5000000; defparam unitclk1ms.

N = 23; endmodule. In the listing port ‘addr’ (Line 23) is 2 bit wide as ‘addrwidth’ is set to 2 (Line 17). Therefore, total ‘4 elements (i.e. 2^2)’ can be stored in the RAM. Further, ‘din’ port (Line 24) is 3 bit wide as ‘datawidth’ is set to 3 (Line 18); which means the data should be 3 bit wide.

In summary, current RAM-designs can store ‘4 elements’ in it and each elements should be 3-bit wide (see declaration at Line 28 as well).Write enable (we) port should be high and low for storing and retrieving the data respectively. ‘din’ port is used to write the data in the memory; whereas ‘dout’ port is used for reading the data from the memory. In Lines 32-33, the write operation is performed on rising edge of the clock; whereas read operation is performed at Line 37.Lastly, Fig. Shows the simulation results for the design. Here, ‘we’ is set to 1 after first cursor and the data is written at three different addresses (not 4). Next, ‘we’ is set to 0 after second cursor and read operations are performed for all addresses.

Since, no values is stored for address ‘10’, therefore dout is displayed as ‘UUU’ for this address as shown after third cursor. // singleportRAMvisualTest.v // created by: Meher Krishna Patel // date: 26-Dec-16 // Functionality: // store and retrieve data from single port RAM // ports: // Write Enable (we): SW16 // Address (addr): SW15-14 // din: SW2:0 // dout: LEDR module singleportRAMvisualTest #( parameter ADDRWIDTH = 2, parameter DATAWIDTH = 3 ) ( input wire CLOCK50, input wire 16: 0 SW, output wire DATAWIDTH - 1: 0 LEDR ); singleportRAM singleportRAMtest (. Clk ( CLOCK50 ),. We ( SW 16 ),. Addr ( SW 15: 14 ),.

Din ( SW 2: 0 ),. Dout ( LEDR ) ); endmodule. 8.8 Dual port RAMis used to implement Fig., which is same as with three changes. First, two address ports are used at Line 25 (i.e. ‘addrrd’ and ‘addrwr’) instead of one. Next, ‘addrwr’ is used to write the data at Line 35; whereas ‘addrrd’ data is used to retrieve the data at Line 39. Hence, read and write operation can be performed simultaneously using these two address lines.Fig.

Shows the simulation results for dual port RAM. Here, on the first cursor, ‘011’ is written at address ‘01’. On next cursor, this value is read along with writing operation as location ‘10’. Lastly, last two cursor shows that if read and write operation is performed simultaneously on one address e.g.

‘01’, then new data will be available at ‘dout’ port after one clock cycle. // dualportRAMvisualTest.v // created by: Meher Krishna Patel // date: 26-Dec-16 // Functionality: // store and retrieve data from single port RAM // ports: // Write Enable (we): SW16 // Address (addrwr): SW15-14 // Address (addrrd): SW13-12 // din: SW2:0 // dout: LEDR module dualportRAMvisualTest #( parameter ADDRWIDTH = 2, parameter DATAWIDTH = 3 ) ( input wire CLOCK50, input wire 16: 0 SW, output wire DATAWIDTH - 1: 0 LEDR ); dualportRAM dualportRAMtest (. Clk ( CLOCK50 ),. We ( SW 16 ),. Addrwr ( SW 15: 14 ),. Addrrd ( SW 13: 12 ),. Din ( SW 2: 0 ),.

Dout ( LEDR ) ); endmodule. //ROMsevenSegment.v // created by: Meher Krishna Patel // date: 25-Dec-16 // Functionality: // seven-segment display format for Hexadecimal values (i.e. // ROMsevenSegmentvisualTest.v // created by: Meher Krishna Patel // date: 25-Dec-16 // Functionality: // retrieve data from ROM and display on seven-segment device and LEDs // ports: // SW: address in binary format // HEX0: display data on seven segment device // LEDR: display data on LEDs module ROMsevenSegmentvisualTest ( input wire 3: 0 SW, output wire 6: 0 HEX0, output wire 6: 0 LEDR ); // signal to store received data, so that it can be displayed on // two devices i.e. Seven segment display and LEDs wire 6: 0 data; ROMsevenSegment sevensegmentROM (. Addr ( SW ),.

4 Bit Parallel In Serial Out Shift Register Verilog Code For 10

Data ( data ) ); assign HEX0 = data; // display on seven segment devices assign LEDR = data; // display on LEDs endmodule. // queuetop.v // write the 'count' from 'modMCounter' to the queue. // SW0: read operation // LEDR0: queue empty // SW1: write operation // LEDR 1: queue full // Test: // 1. Keep reset high, SW1 low and SW0 high till LEDR0 glow, i.e. // queue is empty now. Now, keep SW1 high, SW0 low, then bring reset to low. // Now count will start and will be stored in the queue.

Verilog Code For Piso Shift Register Using D Flip Flop

Bring the SW1 to low again and see the count at // that time (as count will continue to inrease). Now, set SW0 high, and it will start the count from 0, to the count which was // displayed in step 3; and after that LEDR0 will glow again. Next, bring SW0 to low and SW1 to high, and let it run. // after 16 count (i.e. 2^addresswidth), the queue will be full and // LED1 will glow. Module queuetop ( reset, CLOCK50, SW, LEDG, LEDR ); input wire reset; input wire CLOCK50; input wire 1: 0 SW; output wire 3: 0 LEDG; output wire 17: 0 LEDR; wire clk1s; wire 3: 0 count; assign LEDR 17: 14 = count 3: 0 ; // clock 1 sec clockTick unitclkTick (.

Clk ( CLOCK50 ),. Reset ( reset ),. ClkPulse ( clk1s )); defparam unitclkTick. M = 50000000; defparam unitclkTick. N = 26; // queue.v queue unitqueue (.

Clk ( clk1s ),. Reset ( reset ),.

Readcmd ( SW 0 ),. Writecmd ( SW 1 ),. Writedata ( count ),. Full ( LEDR 1 ),. Empty ( LEDR 0 ),. Readdata ( LEDG )); defparam unitqueue. Addresswidth = 4; defparam unitqueue.

Datawidth = 4; defparam unitqueue. Maxdata = 16; // mod-12 counter modMCounter unitcounter (.

Serial In Serial Out Shift Register Pdf

Clk ( clk1s ),. Reset ( reset ),.

Count ( count )); defparam unitcounter. M = 12; defparam unitcounter. N = 4; endmodule.